This is a topic that cover wast applications ranging from Ultrasound devices to RF infrastructure.

In this tutorial we cover some of the aspects of designing interleave ADC from theoretical point of view.

Pipeline adc aimed to be used in application with high data rate and low latency (compare to CT Sigma delta ADC or SAR ADC).

The frequency range for these devices goes from 10Ms/sec up to 64 Gs/sec. Our design is on the range of 125 to 500Ms/sec with 12-14 bit accuracy.

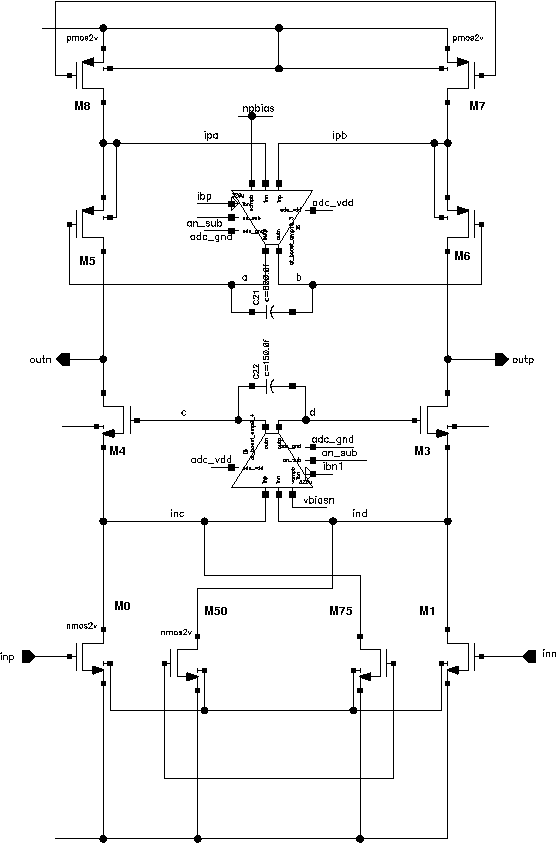

Our design include Sample & Hold that allows to mitigate some of the problems mentioned in the tutorial. Some of the design techniques used here are not traditional balance stage as shown in fig 1.